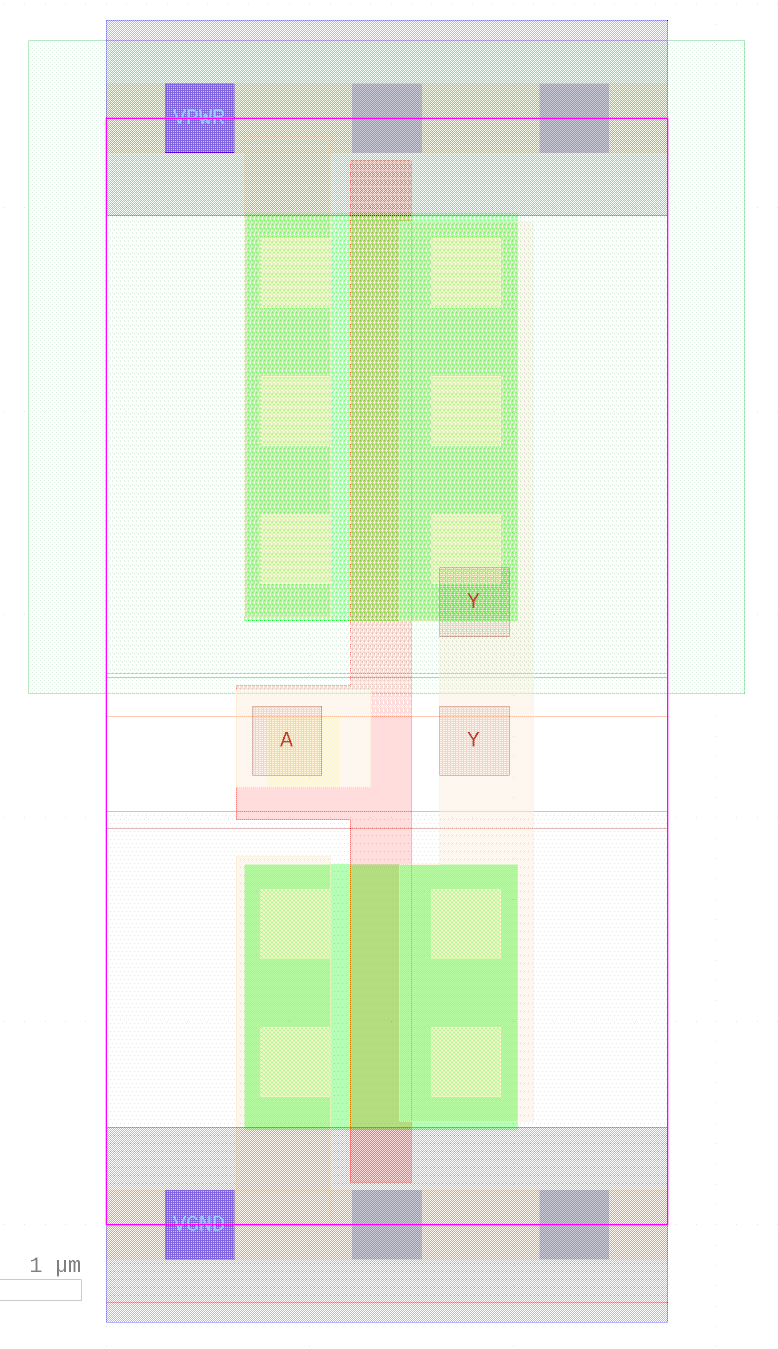

One of the many things a PDK contains is the standard cell library. This is a collection of all digital building blocks used to build an IC like AND, OR, NOT gates, flip-flops, etc. There will be other libraries for specialised functions such as IO pads, and any analogue blocks or memory macros, and so on. Standard cell libraries are a set of cells that have common characteristics and physical layout.| Zero to ASIC Course

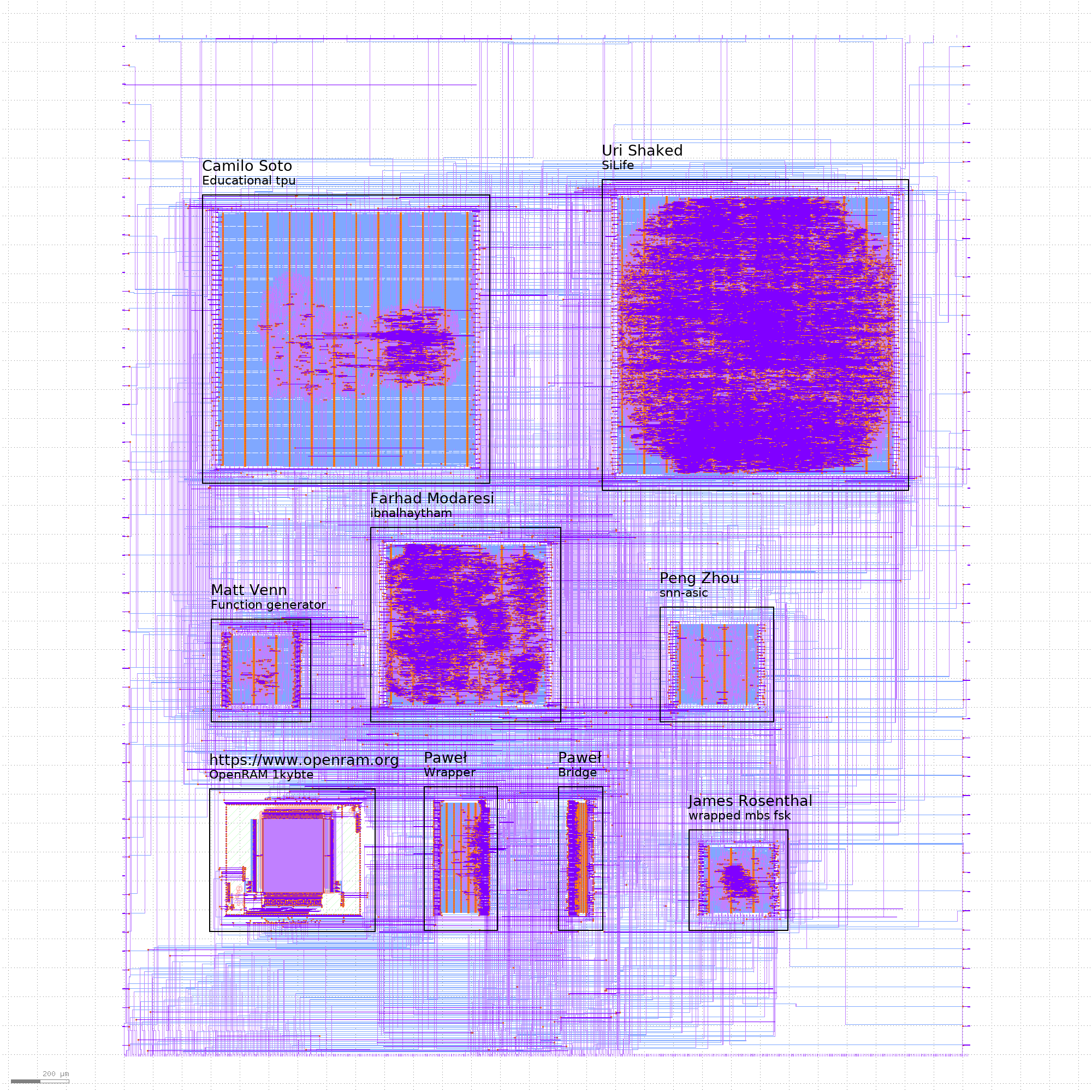

We submitted for MPW7! I am particularly excited about this submission because we were able to submit the Zero to ASIC course designs as well as the first TinyTapeout design. MPW7 has by far had the most submissions of the MPW shuttles so far with 72 submitted projects as of 13 September. Congratulations to everyone on the course submission! We had 9 projects from the course, with 1 demo arbitrary function generator from me, a 32-bit RISC-V based processor by Farhad, an in silicon version of ...| Zero to ASIC Course