It can be challenging to test your FPGA or ASIC graphics designs. You can perform low-level behavioural simulations and examine waveforms, but you also need to verify how the video output will appear on the screen. By combining Verilator and SDL, you can build Verilog simulations that let you see your design on your computer.| Project F

Hardware design can be unforgiving, so it pays to use any advantage you can get. Verilator is a Verilog simulator and C++ compiler that also supports linting: statically analysing your designs for issues. Not only can Verilator spot problems your synthesis tool might overlook, but it also runs quickly.| Project F

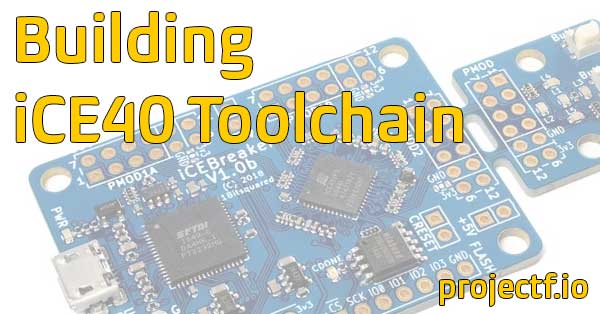

In this post, I provide a quick guide to building an open-source FPGA toolchain for iCE40 boards, such as iCEBreaker, on Linux. This guide is designed for Ubuntu or Pop!_OS 20.04, but should be straightforward to adjust to your own distro.| Project F