Are you tired of firing up the Vivado GUI to build an FPGA project? You can automate your Xilinx FPGA build using a little Tcl. And you don’t even need to know any Tcl. Building your design from a script also comes in handy for continuous integration (CI) and Makefiles. Plus, I’ll show you how to quickly program your dev board with openFPGALoader.| Project F

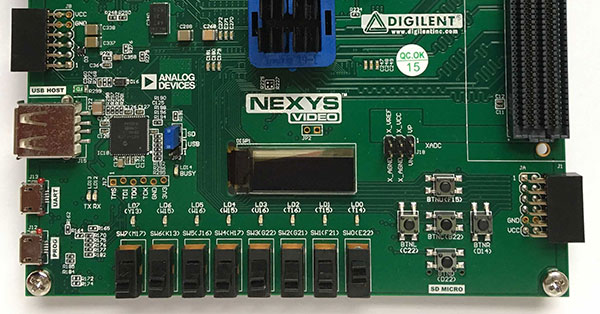

This two-part tutorial provides a quick introduction to FPGA development with SystemVerilog and the Digilent Nexys Video board. No prior experience of FPGA development is required, but basic knowledge of programming concepts is assumed. If you can write a simple program with Python or JavaScript, you shouldn’t have any trouble.| Project F

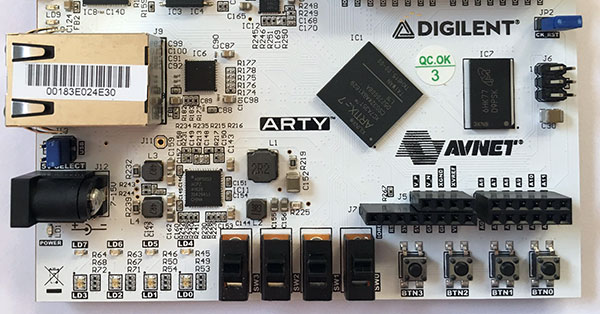

This three-part tutorial provides a quick introduction to FPGA development with SystemVerilog and the Digilent Arty A7 board. No prior experience of FPGA development is required, but basic knowledge of programming concepts is assumed. If you can write a simple program with Python or JavaScript, you shouldn’t have any trouble.| Project F

It’s common for a simulation or firmware to need data loading into a memory array, ram, or rom. Fortunately, Verilog provides the $readmemh and $readmemb functions for this very purpose. Unfortunately, there is a dearth of good Verilog documentation online, so using them can be harder than it should be. This how to explains the syntax and provides plenty of examples, including how to do this in Yosys and Xilinx Vivado.| Project F